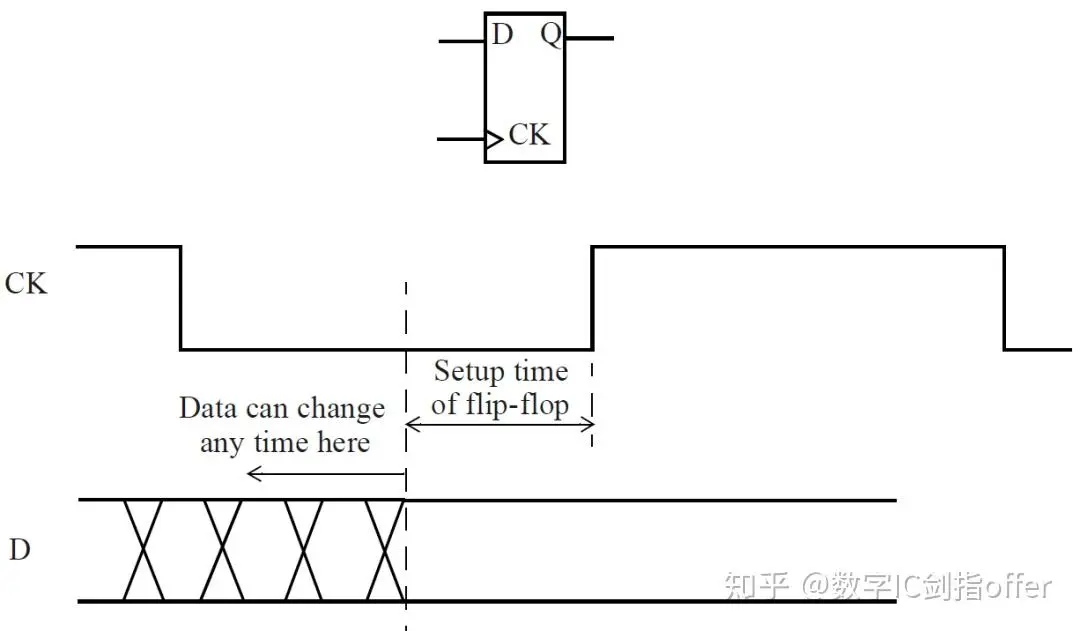

一、时序约束的目的由于实际信号在FPGA内部期间传输时,由于触发器等逻辑期间并非理想期间,因此不可避免地存在传输延时,这种延迟在高速工作频率、高逻辑级数时会造成后级触发器地建立时间和保持时间不满足,造成时序违例。(这也是为什么需要把FPGA设计不能以高级编程...

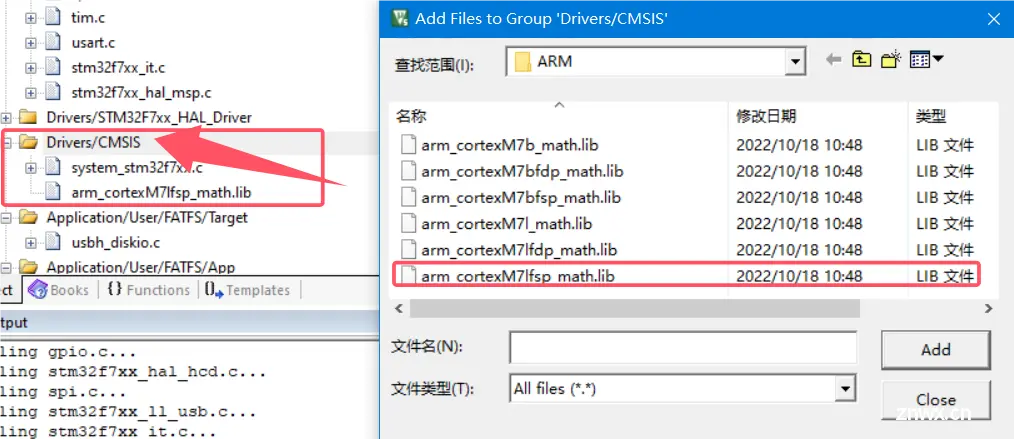

最近在学习如何在STM32中调用FFT。_stm32fft...

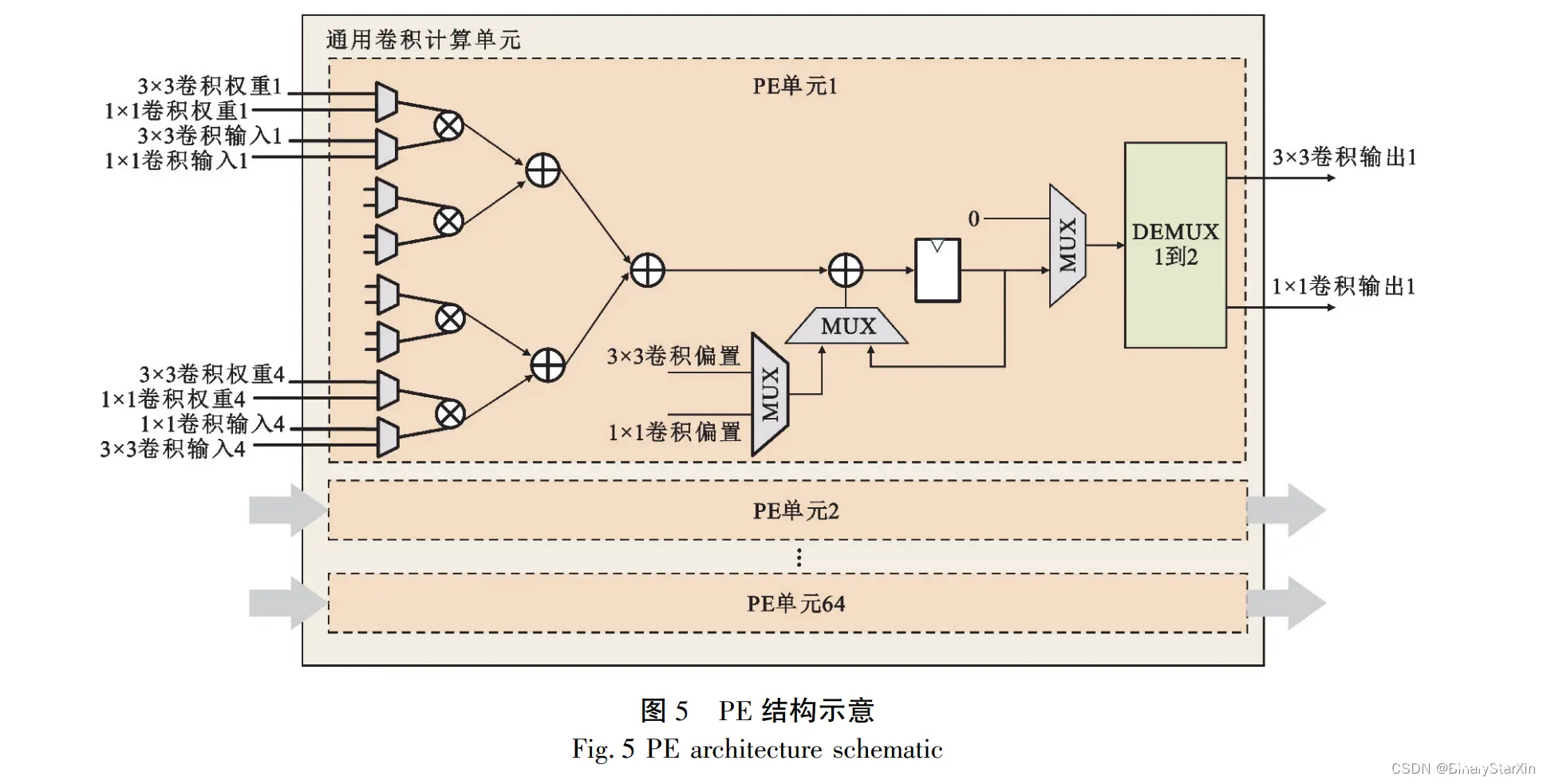

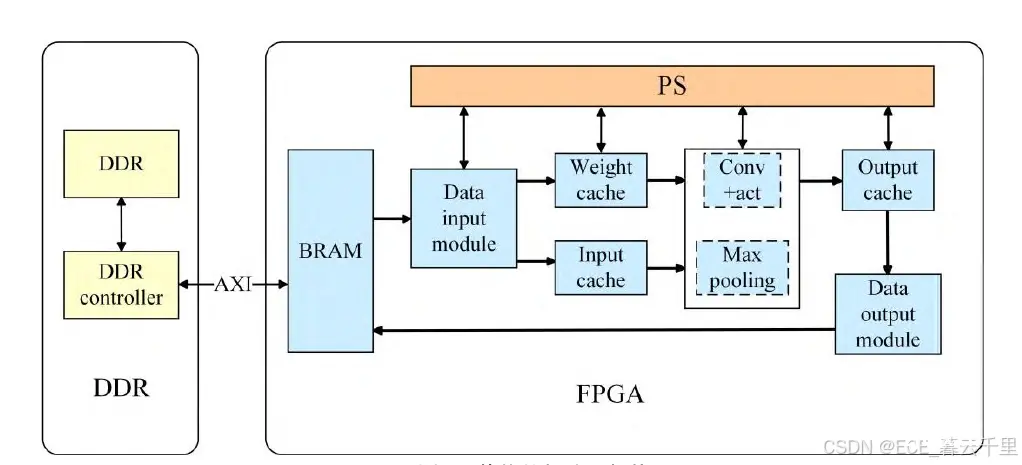

针对资源受限的嵌入式平台,本文提出了一种FPGA上的YOLOv5s目标检测网络加速结构,通过共享1×1和3×3卷积计算单元提高硬件资源利用率。该结构结合了卷积层融合、量化、循环分块和双缓冲策略,以提升计算效率和减...

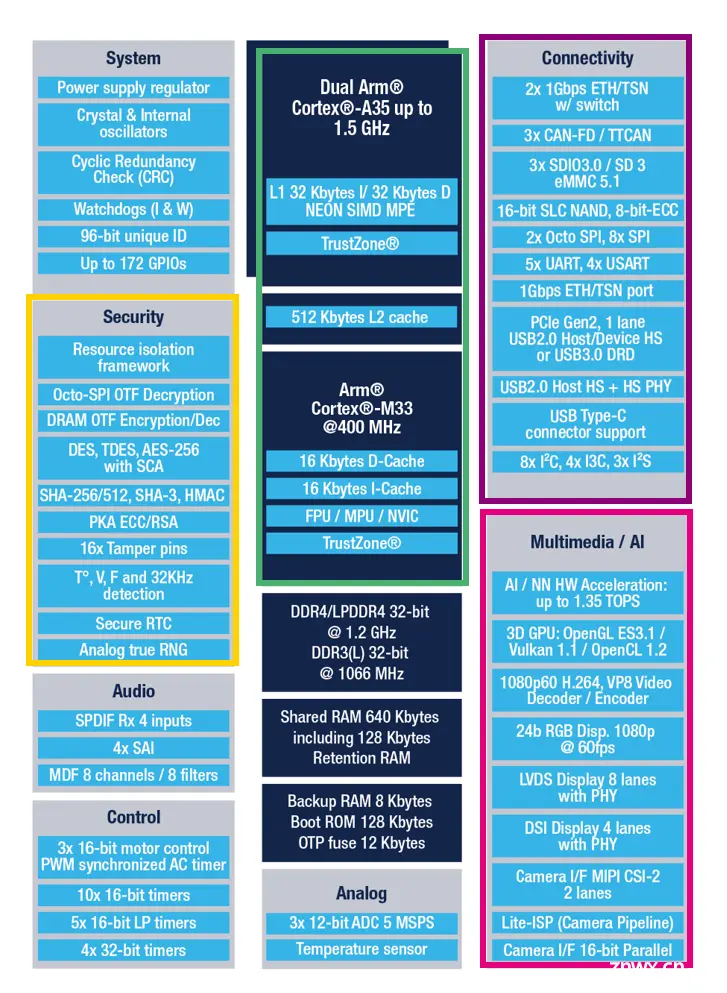

Cortex-M33核不仅具备直接访问片上SRAM资源的能力,还能够高效地访问板载DDR存储,运行基于裸机或实时操作系统(RTOS)的硬实时等关键应用时,能够享有高数据吞吐率和充足的内存资源,从而确保系统的高效运行...

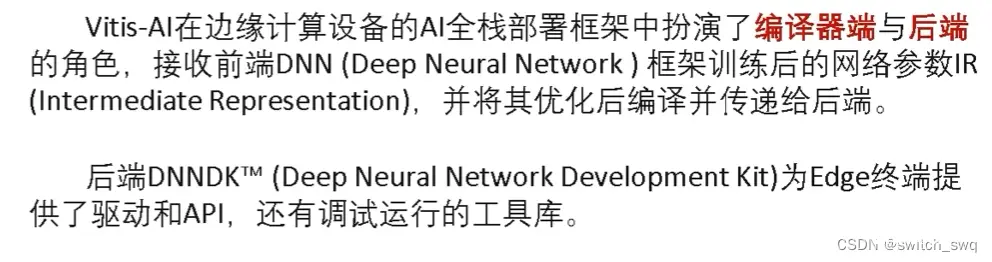

边缘计算edge-ai;edge端inference全栈部署方案。_vitis-ai...

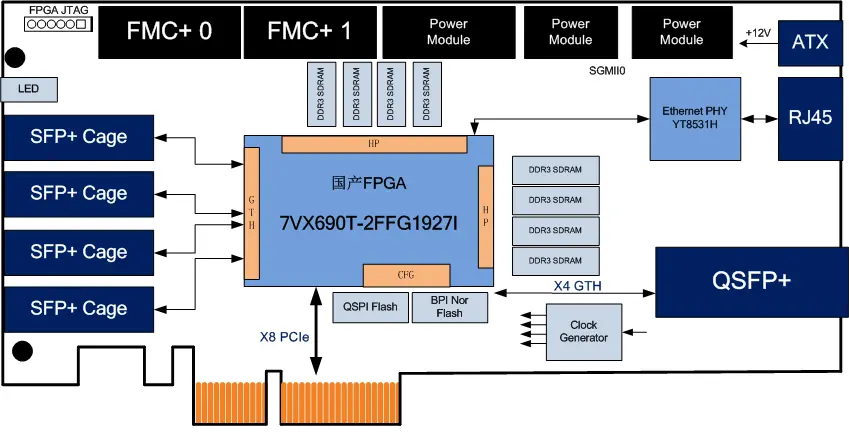

基于国产28nm7系列FPGA7VX690T的全国产化8通道光纤双FMC接口数据预处理平台,该板卡采用高性能7系列FPGA作为实时处理器,实现4路10GSFP+光纤以及1路QSFP+通信接口、实现1路X8PC...

【人工智能】FPGA实现人工智能算法硬件加速学习笔记...

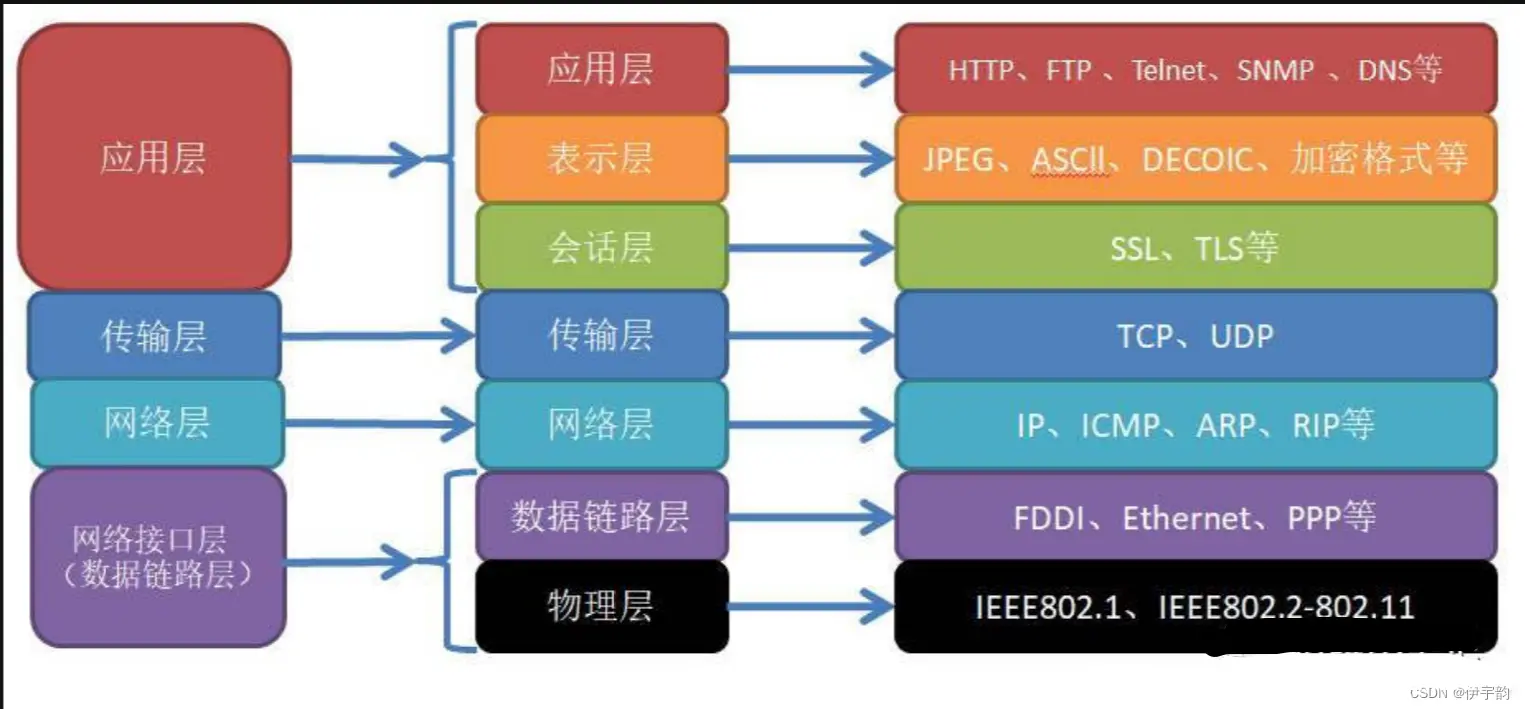

以太网是现实世界中最普遍的一种计算机网络。以太网有两类:第一类是经典以太网,第二类是交换式以太网,使用了一种称为交换机的设备连接不同的计算机。经典以太网是以太网的原始形式,运行速度从3~10Mbps不等;而交换...

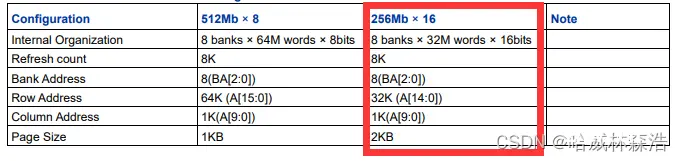

DDR3管脚根据不同的功能可以分为:数据组、地址组、控制组和电源组。如图上所示,共96个管脚。_ddr3脚位...

AI系统是一个集成了硬件、软件和数据,用于执行人工智能任务的复杂系统。它涵盖了从数据收集、预处理、模型训练、推理到最终应用部署的整个过程。AI系统的核心在于通过机器学习算法和深度学习模型,使计算机能够模拟人类的智...