GPIO简介

RAM-YAO 2024-07-30 16:15:00 阅读 60

基于STM32F4xx中文参考手册进一步的手册内容分析

目录

- GPIO简介

- GPIO主要特性

- GPIO功能描述

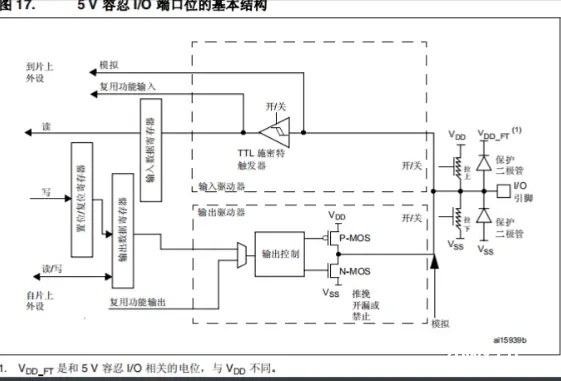

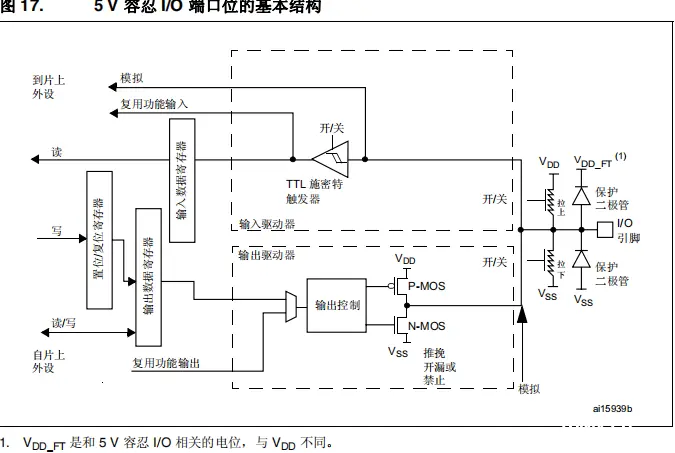

- I/O 端口位的基本结构

以下是基于STM32F4xx中文参考手册进一步的手册内容分析,作为自身学习过程的记录。如您是初学者并且对手册描述的内容感到一知半解,您可以参考以下部分内容并结合您自身的见解加深对相关内容的理解。若是大佬们看到内容有误导方向的,欢迎大佬指出!在避免误导他人的前提下自身也在学习进步,谢谢!!

GPIO简介

GPIO(General Purpose Input/Output)外设是微控制器中最基本且最通用的接口,用于与外部设备进行交互。GPIO引脚的核心功能是作为通用的数字输入或输出,可以通过软件配置为多种工作模式,以满足不同的应用需求,GPIO引脚需要和外设连接在一起,可以和外设实现通信以及采集数据等功能。

对于STM32F4xx系列来说每个通用 I/O 端口包括 4 个 32 位配置寄存器(GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR 和 GPIOx_PUPDR)、2 个 32 位数据寄存器(GPIOx_IDR 和GPIOx_ODR)、1 个 32 位置位/复位寄存(GPIOx_BSRR)、1 个 32 位锁定寄存器(GPIOx_LCKR) 和 2 个 32 位复用功能选择寄存器(GPIOx_AFRH 和 GPIOx_AFRL)。

注意:如果您使用的是STM32F10x系列它对应的寄存器是有所区别的,您需要根据具体的手册进行区分。

GPIO主要特性

受控 I/O数量:受控 I/O 多达 16 个,如PA0-PA15。

输出输入状态:推挽或开漏输出 + 上拉或下拉输入。

推挽与开漏输出比较明显的区别就是推挽模式对高低电平均有输出能力,开漏模式只对低电平具有输出能力,对高电平呈现为高阻态。推挽模式的电平驱动能力强于开漏模式,这也使得使用推挽模式相对于开漏模式产生的功耗更高。而由于开漏模式对高电平具有高阻态的这一特性,通常可以用于在IIC通信的配置当中,可以避免高低电平的冲突导致短路。

上拉与下拉的区别则是在没有电平输入时,电平由上拉或者下拉电阻来决定默认的电平状态。如果为上拉模式,默认电平则由上拉电阻拉高至高电平。如果为下拉模式,默认电平则由下拉电阻拉低至低电平。

输出数据方式:从输出数据寄存器 (GPIOx_ODR) 或外设(复用功能输出比如定时器、串口等输出)进行输出数据。

输入数据方式:将数据输入到输入数据寄存器 (GPIOx_IDR) 或外设(复用功能输入比如定时器的输入捕获功能)。

IO口速度:可为每个 I/O 选择不同的速度。通常有低速、中速、高速等速率。当输出速度配置越高,则意味着GPIO引脚可以更快的切换输出电平状态。当IO口为输入模式时引脚的关键点通常是输入电平单的稳定性,而不是输出速度,输出速度对于输入模式并不适用与无实际意义。每次翻转最快只需要两个时钟周期。

**锁定机制 **:(GPIOx_LCKR),可冻结 I/O 配置。当需要确保某个IO口的配置不被意外的改变(比如输入输出模式、复用功能等)可以通过 GPIOx_LCKR寄存器冻结该IO口的配置,这可以防止在运行时意外的改变IO口的配置导致的系统不稳定。

模拟功能:通常用于ADC转换的模拟输入时使用。

GPIO功能描述

可通过软件将通用 I/O (GPIO) 端口的各个端口位分别配置为8种工作模式:

1.输入浮空

2.输入上拉

3.输入下拉

4.模拟功能

5.具有上拉或下拉功能的开漏输出

6.具有上拉或下拉功能的推挽输出

7.具有上拉或下拉功能的复用功能推挽

8.具有上拉或下拉功能的复用功能开漏

I/O 端口寄存器必须按 字(32 位)、半字(16位)或字节(8位)进行访问。

GPIOx_BSRR(端口置位复位寄存器)旨在实现对 GPIO_ODR(端口输出数据寄存器)进行原子读取/修改访问。这样便可确保在读取和修改访问之间发生中断请求也不会有问题。

以下列出了不同功能模式的简单特征描述:

| 模式名称 | 性质 | 特征 |

|---|---|---|

| 浮空输入 | 数字输入 | 可读取引脚电平,若引脚悬空,则电平不确定 |

| 上拉输入 | 数字输入 | 可读取引脚电平,内部接上拉电阻,悬空时默认高电平 |

| 下拉输入 | 数字输入 | 可读取引脚电平,内部接下拉电阻,悬空时默认低电平 |

| 模拟输入 | 模拟输入 | GPIO无效,引脚直接接入内部ADC |

| 开漏输出 | 数字输出 | 可输出引脚电平,高电平为高阻态,低电平接到VSS |

| 推挽输出 | 数字输出 | 可输出引脚电平,高电平接VDD,低电平接VSS |

| 复用开漏输出 | 数字输出 | 由片上外设控制,高电平为高阻态,低电平接VSS |

| 复用推挽输出 | 数字输出 | 由片上外设控制,高电平接VDD,低电平接VSS |

I/O 端口位的基本结构

首先先确定一下看图方向,当为输入时,看图顺序应当为从右到左,观看上半部分。当为输出时看图顺序应当为从左到右,观看下半部分。

输入部分分析

首先我们可以先看到两个保护二极管,这两个二极管是起到限流作用的,当输入电压过大那么上方的保护二极管则会导通,电压不会流入内部电路,从而起到保护电路的作用。当输入电压比0V还要低也就是负电压时,下方的保护二极管则会导通进行保护电路。接着看到上拉与下拉电阻,此时电平的输入是不确定的浮空状态,STM32就是通过这两个内部的电阻进行将浮空状态变为确定状态的电平状态。此时的流向经过到了TTL施密特触发器,什么是施密特触发器?

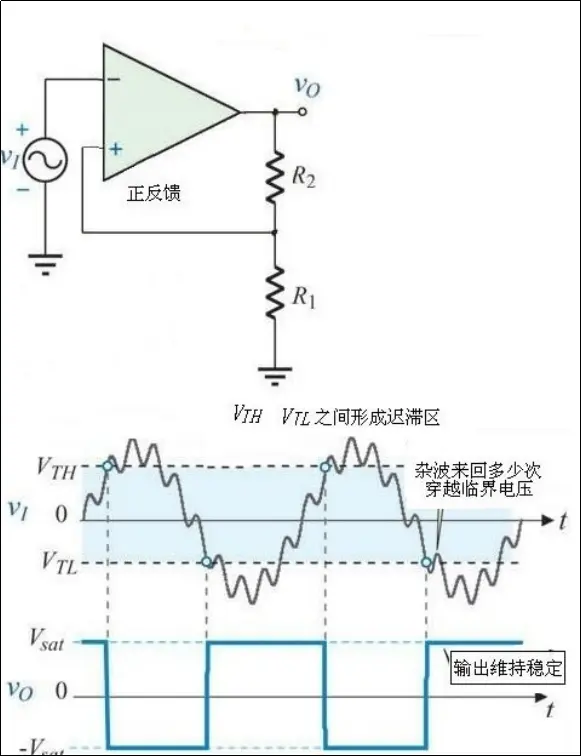

这里的TTL施密特触发器其实是对输入电压进行整平的,从而能够输出规整的方波矩形。施密特触发器输入电压有两个阈值VL、VH,用做缓冲器消除输入端的噪声干扰。当任何波形的信号进入电路时,输出在正负饱和之间跳动,当未达到上下阈值时输出电压不会发生变化,从而避免了额外的信号干扰造成误触发电路。以下为施密特触发器的简图。

可以看到当输入电压VI大于上限阈值VTH时触发电路会使得VO的输出转态,当输入电压VI小于下限阈值VTL时触发电路也会使得VO的输出转态,通过这样的特性就能够消除部分噪声造成的干扰。

在施密特触发器的之前有一个模拟输入,为什么要在施密特触发器之前接入模拟输入呢?原因是模拟输入接收的是模拟量,不需要使用施密特触发器进行电压整平,所以接到施密特触发器之前,接收未整平过的电压模拟值,而施密特触发器之后接收的是数字量的电平输入所以在施密特触发器之后。经过施密特触发器后输入就到了输入数据寄存器了,通过读取输入数据寄存器就能知道端口此时的电平了。

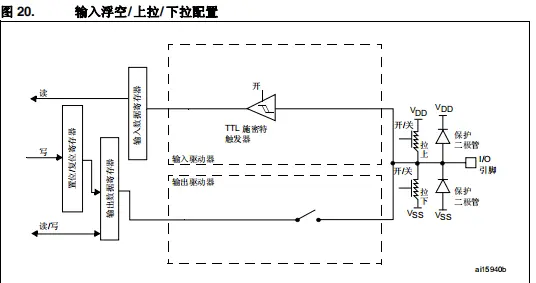

上面说过输入模式有浮空/上拉/下拉/模拟输入模式,可以再对输入模式进行一点细致分析。

此时我们还可以看到,在输入模式下,其实输出驱动器是断开的,也就是输入模式下是无法进行输出的。

此时可以看到输出缓冲器被禁止。

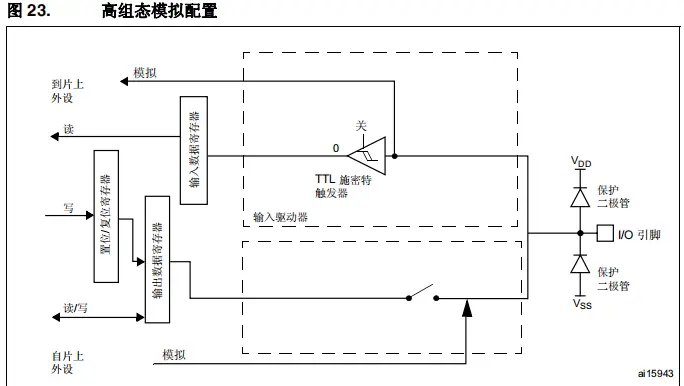

施密特触发器输入停用,I/O 引脚的每个模拟输入的功耗变为零。施密特触发器的输出被

强制处理为恒定值 (0)。

弱上拉和下拉电阻被关闭。

对输入数据寄存器的读访问值为“0”。

注意: 在模拟配置中,I/O引脚不能为5V容忍,这是因为内部的ADC是一个12位的模数转换器,参考电压为3.3V。

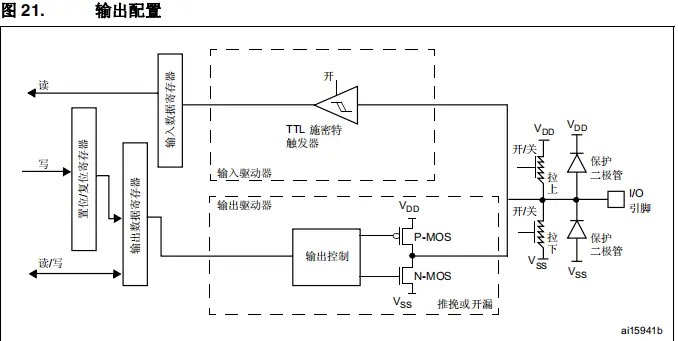

输出部分分析

输出部分可以由输出数据寄存器和片上外设(即芯片上的一些硬件外设)进行控制,此时通过选择器到达输出控制器,这里遇到了两个MOS管,这两个MOS管是用来做开关作用的。上面我们说过输出模式有推挽输出模式与开漏输出模式。

推挽输出下高低电平均有驱动能力,此时这里的PMOS与NMOS管均有效,当输出高电平时上管PMOS导通,下管NMOS断开输出直接接到VDD,也就是直接输出高电平了,当输出低电平时下管导通上管断开下管接到VSS输出低电平。

开漏模式下对输出高电平具有高阻态,只对低电平具有驱动能力,所以就PMOS管始终是断开的。

为什么输入高低电平PMOS,NMOS就相应的导通断开?

其实我们可以将PMOS管想象成NPN型三极管,我们知道NPN型三极管当基极给一高电平时会导通,同理就是为什么当输出控制器给一高电平PMOS就导通了。而NMOS管可以将其看成是PNP型三极管,PNP型三极管当基极给一低电平就会导通,同理输出控制器给一低电平NMOS就导通了。(注意这里只是一种比喻的形式,三极管与MOS管并不等同即PMOS管并不等同就是NPN型三极管只是将它们的一个特点就行了一个联系以比喻帮助理解,若想更加深入的了解二者的区别建议读者去查阅相关模电书籍!!!)

经过MOS管后就能将输出电压输出到IO引脚了,将相应传感器接到对应引脚就能实现控制了。

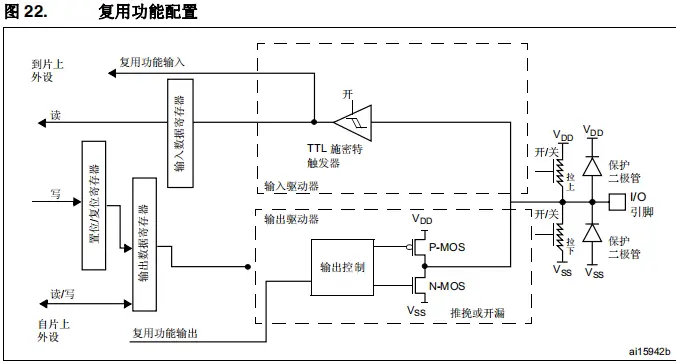

上面说过输出其实有推挽/开漏输出,以及复用推挽/开漏输出模式。也可以再细致分析一下。

在推挽/开漏输出的模式下,有如下图:

此时的输出来自输出数据寄存器,可以看到输出模式下输入部分是有效的,因为一个端口只能有一个输出,但可以有多个输入。也就是说其实在配置为输出模式时,内部也可以顺便读取一下输入的电平状态,建议在需要读取输入电平时采取输入模式较好。

在复用推挽/开漏输出的模式下,有如下图:

此时普通IO输出被断开,引脚的控制权转移到了片上外设,由片上外设控制。即由外设控制引脚的输出状态,如定时器、串口、IIC、SPI等片上外设。

以上8种模式中只有模拟输入会关闭IO口的输入功能,其他模式的输入功能都是有效的。

声明

本文内容仅代表作者观点,或转载于其他网站,本站不以此文作为商业用途

如有涉及侵权,请联系本站进行删除

转载本站原创文章,请注明来源及作者。