时序分析基本概念介绍——SI/crosstalk/delta delay/noise/timing Window

芯纪元 2024-08-11 10:05:02 阅读 93

文章目录

前言一、Crosstalk1. Crosstalk Delay Effects2. Crosstalk Noise Effects

二、Crosstalk Analysis1. Crosstalk Delay Analysis2. Crosstalk Noise Analysis

三、如何 fix delta delay 和 noise violations1. 检查delta delay 和 noisedelta delay checknoise check

2. 修复delta delay 和 noise violations

总结

前言

信号完整性(Signal Integrity)指的是在周围高频电磁干扰环境中依然能够保持信号稳定的能力;串扰(Crosstalk)指的是相邻的两条或多条net之间的耦合电容带来的相互影响。随着工艺越来越先进,布线密度越来越高,串扰带来的影响越来越重要。

一、Crosstalk

一般可以把crosstalk 带来的影响分为两类:Crosstalk Delay Effects 和 Crosstalk Noise Effects。

1. Crosstalk Delay Effects

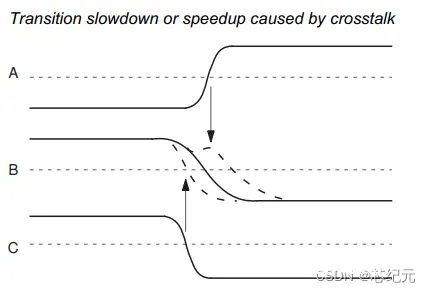

串扰会引入Crosstalk Delay(Delta Delay),通过改变信号的 transitions 来影响信号延迟,如下图所示A和C对B的干扰(slowdown & speedup)。

2. Crosstalk Noise Effects

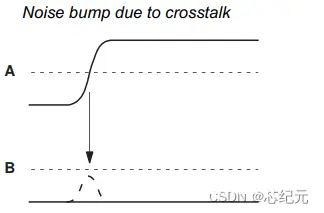

串扰还会引入噪声(Noise),有时也称为毛刺(Glitch)。Static noise通过改变 steady-state nets(稳态0/1的net) 的逻辑跳变来影响功能。

二、Crosstalk Analysis

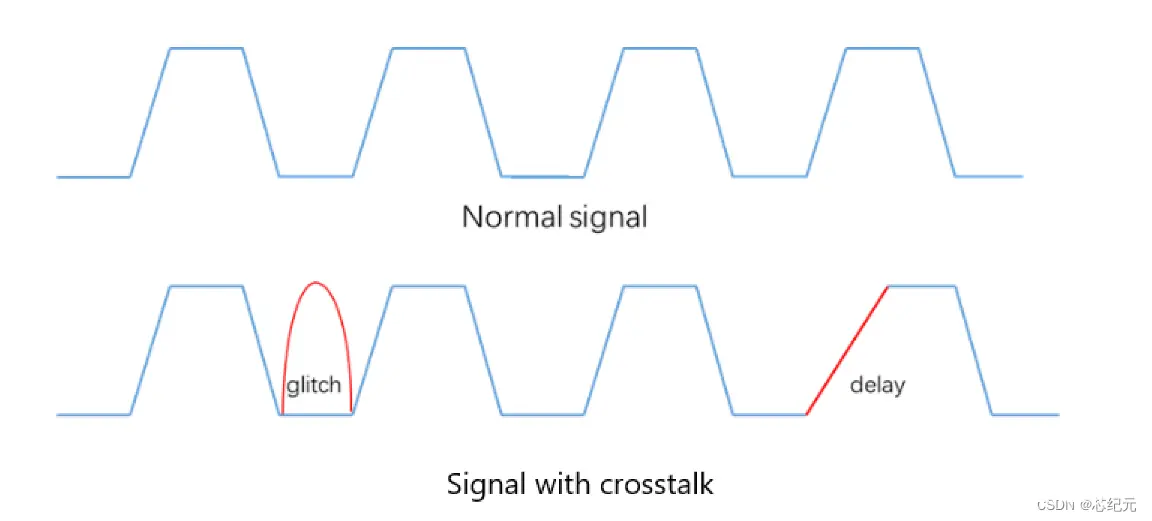

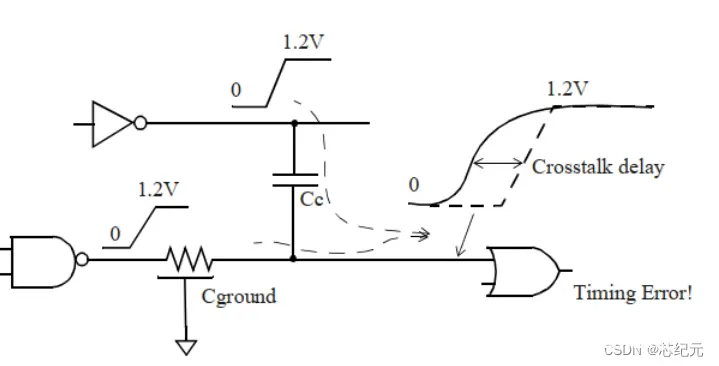

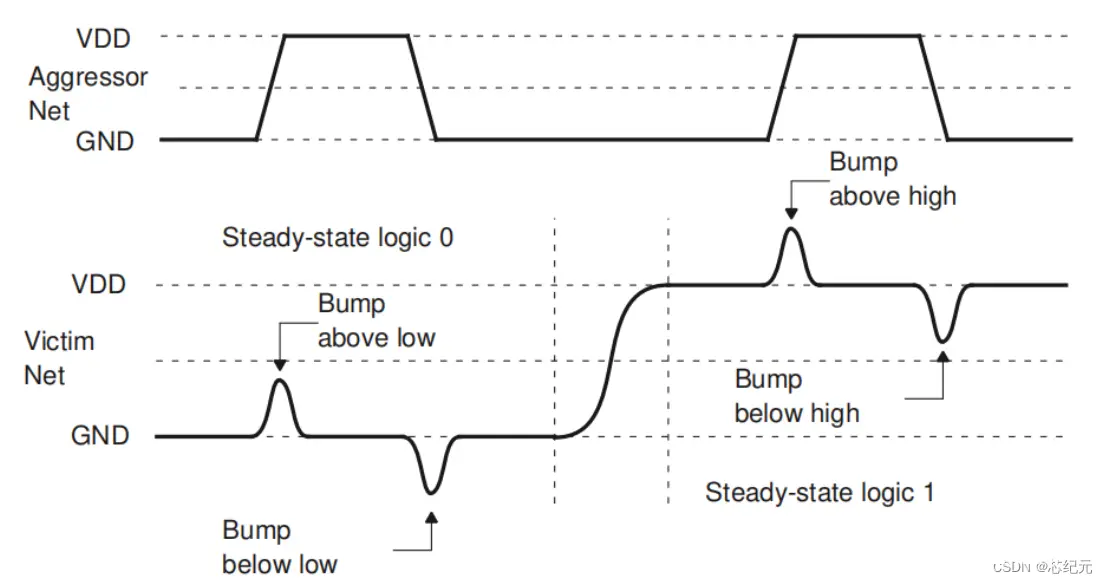

正常波形和收到crosstalk影响的波形如下图所示,delay的增大可能导致timing不满足, 产生的glitch可能会导致信号传输错误。

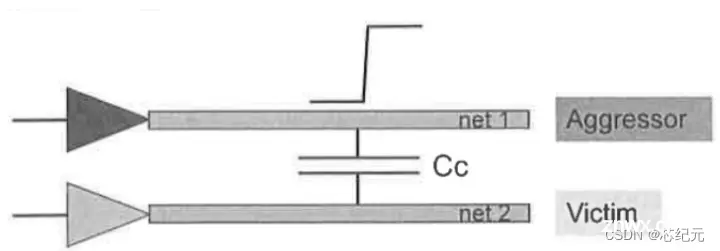

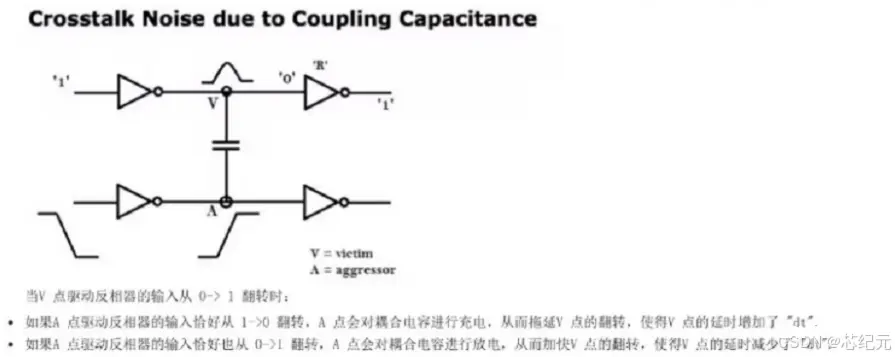

串扰是信号之间的相互影响,两根紧挨着的绕线(net)之间存在耦合电容,当一条线进行电平转换的过程中,另一条线也会受到相应的影响。其中第一条线称为攻击端(aggressor),第二根线称为受害端(victim)。

1. Crosstalk Delay Analysis

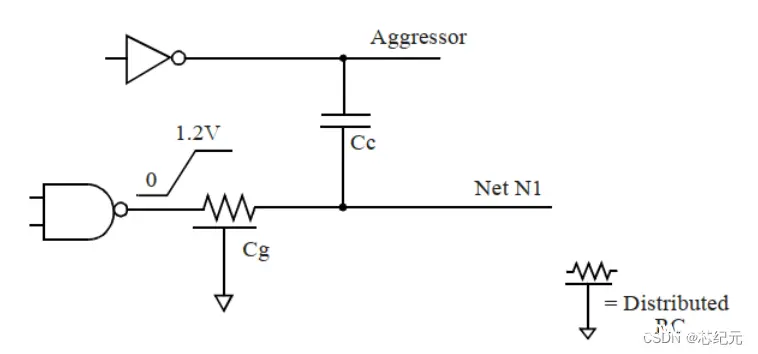

如下图所示Net N1通过电容Cc耦合到相邻的网络(标记为Aggressor Net),并通过电容Cg接地。此示例假定网络N1在输出端具有上升电平过渡,并根据Aggressor Net是否同时进行电平切换来考虑不同的情况。

同时切换Aggressor和Victim的电平会影响Victim网络的过渡时间。根据攻击者网络电平切换方向的不同,串扰延迟影响可能为正(减慢受害者网络过渡时间)或为负(加快受害者网络过渡时间)。

正串扰延迟影响的示例如下图所示。受害者网络在下降的同时,攻击者网络却在上升。攻击者网络向相反方向的电平切换会增加受害者网络的延迟。正串扰(positive crosstalk)会影响驱动单元以及互连线,这两者的延迟都会增加。

串扰延迟为负的情况如下图所示。攻击者网络与受害者网络同时上升,攻击者网络与受害者网络朝相同方向的电平切换可减少受害者网络的延迟。如前所述,负串扰(negative crosstalk)会影响驱动单元和互连线的时序,两者的延迟都会减小。

当Victim Net和Aggressor Net同向翻转时,会加快Victim Net的跳变;当Victim Net和Aggressor Net异向翻转时,会减缓Victim Net的跳变。

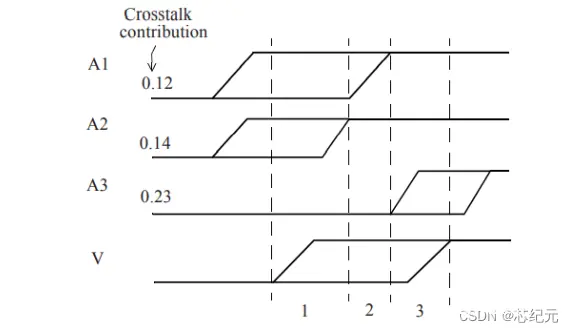

在当前STA方法学中,对于由crosstalk引起的delta delay的计算为:先分别计算Victim Net和Aggressor Net的timing window,如果攻击者和受害者的时间窗口有重叠,就需要计算串扰对延迟的影响。对于多攻击者的情况,多条攻击者的时间窗口也要做类似的分析。时间窗口(Timing Window)表示在1个时钟周期内1条线可以在其中翻转的最早和最晚翻转时间。

如下所示,3个不同的攻击线可以影响受害线的时序。攻击线(A1,A2,A3)和受害线(V)电容性耦合,并且它们的时间窗口也和受害线重叠。下图显示了时间窗口和由各个攻击者造成的可能的串扰延迟影响。基于时间窗口,串扰延迟分析确定了造成大串扰延迟影响的最差可能攻击者翻转组合。在这个例子中,时间窗口的重叠区域可以分为3个区域,每个区域说明了可能的攻击者翻转。区域1有A1和A2电平翻转,可以导致串扰延迟影响为(0.12+0.14)=0.26。区域2有A1电平翻转,可以导致串扰延迟影响为0.14。区域3有A3电平翻转,可以导致串扰延迟影响为0.23。因此,最差串扰延迟影响为区域1的0.26。

Delta delay对setup/hold都是worst的影响。

2. Crosstalk Noise Analysis

如下图所示,由aggressor nets transitions 导致处于 steady-state 的victim net 产生四种不同类型的noise bump:above low、below high、above high、below low。

这四种noise bump可以分成两组:Between-the-rails 和 Beyond-rails。

一般情况下,PTSI 只会考虑Between-the-rails noise bump (即above low、below high),如果超过了规定的阈值,就可能导致一些错误的跳变(这种错误不一定引起真实的功能错误,因为产生的noise bump可能随着电路的传递会逐渐减弱、消失,但也有可能被加强。如果这种错误跳变被一级一级往后传,并且noise bump依然超过阈值,并且被时钟捕获到,则会引起功能错误)。

Beyond-rails noise bump(即above high、below low)也对电路结构有一定的影响,如果这种noise bump直接进到input 没有缓冲单元的flop/latch中,可能会正向偏置击穿gate,进而导致功能错误,但目前的lib 库中的flop/latch都会包含一些缓冲单元,所以这种情况发生的概率比较小。

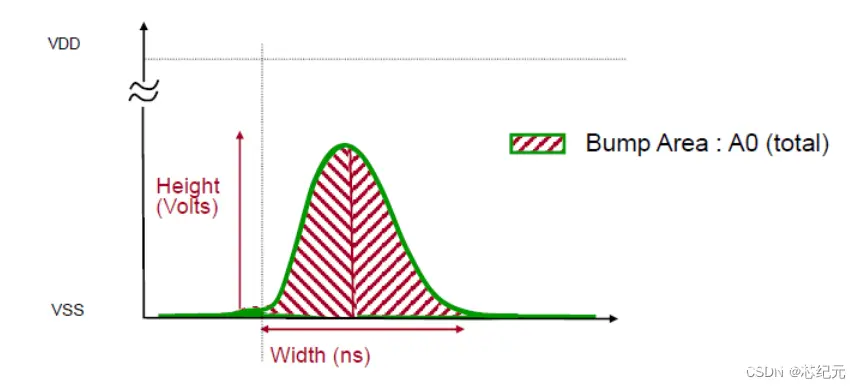

为了进行Noise或者Glitch分析,需要对一个串扰造成的Bump建模,它有宽度和高度,还有面积等属性概念(如下图所示)。

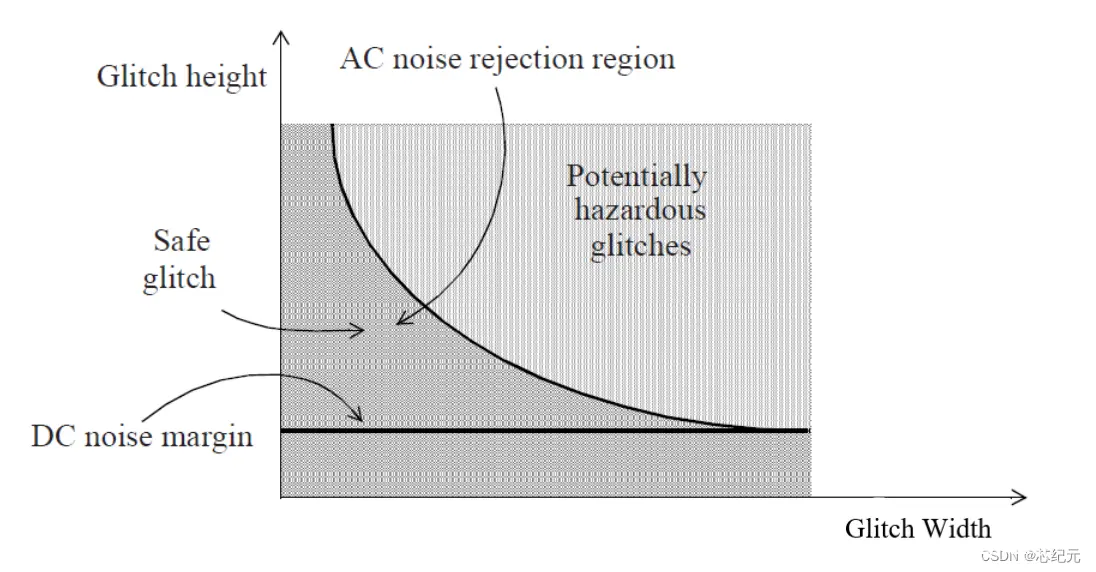

PT-SI在进行update_noise计算时,首先会采用较为悲观的方式快速计算一个类似于下图中DC noise margin的阈值,如果计算出的Bump Height远低于该值,那么就可以断定没有noise不会传播,没有危害。如果计算出的Bump Height接近这个阈值,那么工具就会启动更精细的类似SPICE的门级仿真,取得更精确的结果。通过这种方式,即节省了时间,又保证了精度。

下图中的曲线可以看做是Noise Immunity Curve(NIC),在曲线左下角的Glitch都是无害的,而右上角的Glitch都是必须修复掉的,PT-SI在进行Noise门级仿真时会实时地计算出各个点的NIC。

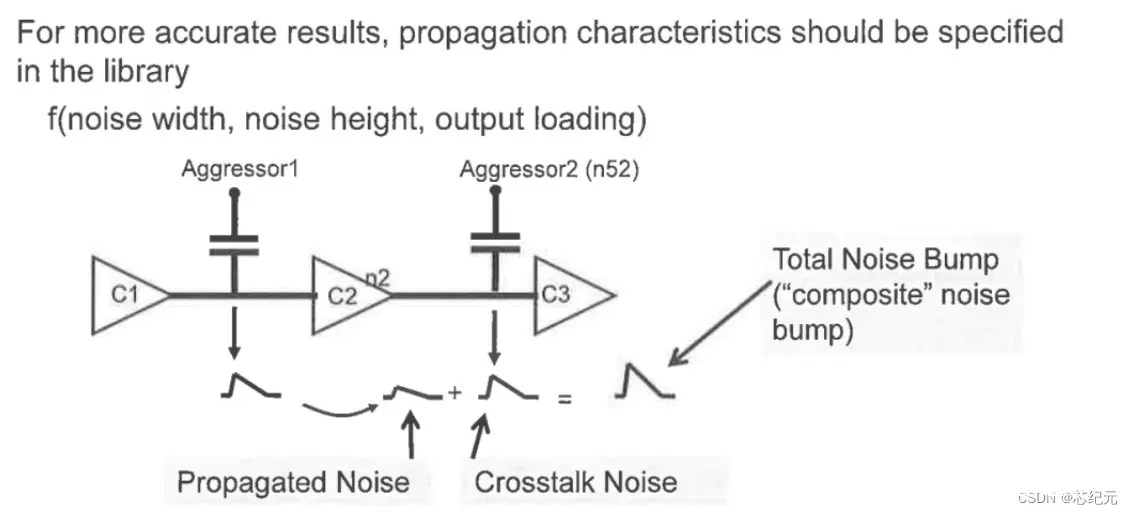

一个cell input 的noise bump 在超过阈值之后可能传输到output 产生一个新的noise bump,这种现象叫做Noise的传播,如下图所示。输出毛刺高度和宽度是输入毛刺的宽度、高度以及输出负载的函数。即输入毛刺形状和输出负载,决定了输出毛刺的形状。而这些函数表征是由标准单元库中的propagated_noise模型描述的。

三、如何 fix delta delay 和 noise violations

在了解了delta delay 和 noise的影响之后,需要将delta delay 和 noise violations报出来,然后修复这些violations。

1. 检查delta delay 和 noise

delta delay check

一般情况下,clock和data的delta delay的阈值设置是不同的,比如data path上面的net的delta delay不超过100ps, clock tree上面的net的delta delay不超过20ps。

因此如果report所有的delta delay violations,首先得到data net和clock net的delta delay,因此需要先通过-filter is_clock_used_as_clock==true判断是data net还是clock net,然后通过 get_attribute $net annotated_delay_delta_max和 get_attribute $net annotated_delay_delta_min来得到delta delay的数值,最后判断delta delay的数值和设置的clock和data的delta delay的阈值的大小,超过阈值的则为delta delay violations。

noise check

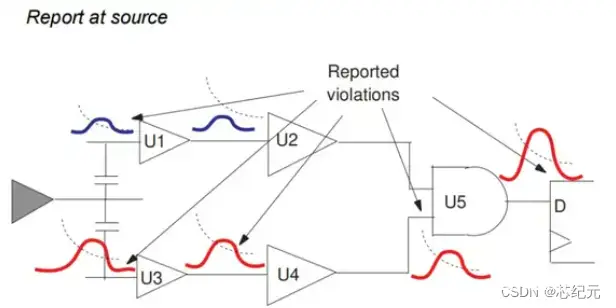

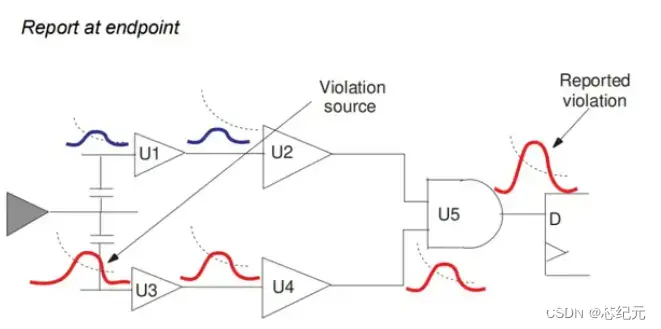

当report noise 的时候有两种mode 供选择,report at source 和report at endpoint。上面说过一个noise bump 超过了阈值不一定会导致最终的功能failure,这跟传输的路径有关系。如下图所示,U1的input nets 受到干扰产生noise bump并超过了要求的阈值,但经过U1的传输,noise bump衰减,低于阈值,那么这种noise bump就不会导致最终的功能failure。report at source会把路径上所有出现violations 的点(noise bump超出阈值)都报出来,报告更加详细;report at endpoint只会报出noise 终止的endpoint,报出来的报告会更加简洁,只显示会引起功能出错的点(一般是flop/latch等)如下图所示。

指令如下:

pt_shell> set_noise_parameters -analysis_mode report_at_endpoint -enable_propagation

report所有的noise violations的指令如下:

pt_shell> report_noise -verbose -all_violators -nosplit

2. 修复delta delay 和 noise violations

修复delta delay 和 noise violations需要结合受害(victim)和攻击(aggressor) Net相关路径的时序,周围Net和Cell的密集程度等情况来具体分析,大致上有以下方法:

(1)增加victim net的驱动单元驱动能力。victim net驱动能力越弱的话,Glitch的量级也会越大。使用髙驱动单元可提髙潜在victim net的门限,从而降低victim net的受害程度。

(2)减少victim net的负载单元驱动能力。

(3)增加victim net和攻击Net的间距。将victim net和aggressor net之间的间距加大,或者采用屏蔽线shielding都是保护victim net的一些好方法。

(4)降低aggressor net的驱动单元驱动能力。aggressor net的驱动能力越强,Glitch的量级就越大。

(5)通过加Buffer将受害Net打断 (工具一般是通过这种方式来修复)。插buffer是后端修复violation的万能手段。它也是是处理noise时一项非常有效的修复技术。通过插入buffer将长线打断能有效降低victim net上的耦合电容,从而降低noise的影响。

总结

在先进工艺节点下,对于STA的check,通常会引入SI(signal integrity)分析。在芯片的电学特性中,时序、串扰和功耗是三项相互相关的重要分析内容。因此,需要了解芯片在物理设施过程中的串扰产生和现象、产生的因素、对芯片引起的危害及实际解决方案等。

声明

本文内容仅代表作者观点,或转载于其他网站,本站不以此文作为商业用途

如有涉及侵权,请联系本站进行删除

转载本站原创文章,请注明来源及作者。