AI嵌入式K210项目(1)-芯片开发板介绍

LinfineEdu 2024-07-05 16:31:02 阅读 79

系列文章目录

在人工智能大潮滚滚而来的时代,作为一个从事嵌入式行业多年的程序猿倍感焦虑,有被替代的焦虑,也有跟不上新技术步伐的无奈,本系列文章将介绍一个从硬件设计到ai训练、最后到模型部署的完整案例;第一阶段我将介绍使用C语言进行裸机开发,在熟悉了硬件和系统之后,我们进入进阶篇,使用MicroPython进行开发;不仅会设计传统的嵌入式技术栈,也有会Python,模型训练,识别分类检测等相关的AI知识;欢迎各位从事嵌入式行业的小伙伴一起学习;

其实,嵌入式和人工智能是相辅相成的,嵌入式系统为人工智能提供了高效的计算和控制平台,使得人工智能算法可以在终端设备上实时运行。而人工智能则可以通过嵌入式系统实现各种智能化功能,如环境感知、人机交互、决策控制等。因此,嵌入式系统和人工智能的结合,可以进一步提高设备的智能化程度和性能。

文章目录

系列文章目录前言一、主控芯片Kendryte K210介绍二、RISC-V结构二、开发板介绍总结

前言

本章将介绍AI嵌入式K210项目所使用的芯片和开发板,有需要的同学可以联系我进行购买V:SpringWa1tz;

一、主控芯片Kendryte K210介绍

Kendryte K210是一颗中国芯,由嘉楠科技设计开发,采用RISC-V处理器架构,具备视听一体、自主IP核与可编程能力强三大特点,支持机器视觉与机器听觉多模态识别,可广泛应用于智能家居、智能园区、智能能耗和智能农业等场景;

Kendryte K210 使用台积电 (TSMC) 超低功耗的 28 纳米先进制程,具有双核64位处理器,拥有较好的功耗性能,稳定性与可靠性。该方案力求零门槛开发,可在最短时效部署于用户的产品中,赋予产品人工智能。

K210具有如下优势:

具备机器视觉能力 具备机器听觉能力 更好的低功耗视觉处理速度与准确率具备卷积人工神经网络硬件加速器KPU,可高性能进行卷积人工神经网络运算 TSMC28nm先进制程,温度范围-40°C到125°C,稳定可靠 支持固件加密,难以使用普通方法破解独特的可编程IO阵列,使产品设计更加灵活低电压,与相同处理能力的系统相比具有更低功耗3.3V/1.8V双电压支持,无需电平转换,节约成本

K210系统架构如下

K210还有哪些特色呐?

K210是基于RISC-V精简指令集的一款MCU,在众多特色中,芯片架构包含了一个自研的神经网络硬件加速器KPU属于最大特色,可以高性能地进行卷积神经网络运算。在MCU的AI计算方面,K210芯片的算力非常给力,根据嘉楠官网的描述,K210的KPU算力能够达到0.8TFLOPS,这相当于什么水平呢?举个例子,最新树莓派4B的算力不到0.1TFLOPS,而以神经网络处理为卖点的Jetson

Nano拥有128个CUDA单元,算力也仅仅是0.47TFLOPS。(这里好像有吹牛的成分,不过应该是性价比较高的支持AI的芯片了,每科芯片只要40块左右)除了KPU的算力优秀之外,K210芯片还有其他一些特色。K210芯片内部是双核CPU,指令集为RISC-V 64位,每个核心内置独立FPU,可以单独进行浮点运算。为了更好地在机器视觉和听觉上发挥作用,K210芯片自带计算卷积人工神经网络加速器KPU,以及处理麦克风阵列的APU,能够进行高性能机器视觉和听觉处理。不仅如此,K210还内置快速傅里叶变换加速器,可以进行复数FFT计算。在性能强劲的前提下,K210芯片还很注重安全性,内置了AES和SHA256算法加速器,为用户的数据安全提供有效保障。再来看看MCU方面的属性,K210芯片具有丰富的外设单元,分别是DVP、JTAG、OTP、FPIOA、GPIO、UART、SPI、RTC、I2S、I2C、WDT、TIMER、PWM,这些外设在实际使用中发挥巨大的作用,基本满足大部分MCU外设的需求。K210还拥有高性能、低功耗的SRAM,总共8M,2M专用于AI计算,6M用于程序;专用外置FLASH接口,增加自身的储存空间;数据传输可使用功能强大的DMA,在数据吞吐能力方面性能优异。

总之K210这款芯片比较便宜,开发板的价格也比较便宜,开发者生态也比较完善,非常适合大家学习;

二、RISC-V结构

顺便做个RISC-V的介绍吧,我觉得国产化替代大潮中,RISC-V架构有可能会和ARM有一战之力;

RISC-V是一个基于精简指令集(RISC)原则的开源指令集架构(ISA)。V表示第五代精简指令集,是加州大学伯克利分校经过前面四代的改良以及升级得来的。该项目开始于2010年的加州大学伯克利分校,后来经过许多贡献者的辛勤耕耘,经过10年‘磨一剑’,RISC-V指令集已经在全球范围内逐渐活跃,相信不久的将来会有更多更好的RISC-V芯片问世。

RISC-V具有以下特点:

完全开源:任何企业都可以自由免费使用RISC-V指令集来制造并营销自己的芯片,而不需要支付高额授权费,并且可以根据自己的需求扩展指令集,自己扩展的指令集不必开放,可以实现差异化发展。架构简单:与主流的X86和ARM架构相比,RISC-V是一个全新的指令集,不需要兼容老旧产品,所以显得格外简洁,整个RISC-V基础指令集只有40多条,加上其他的模块化扩展指令总共也就只有几十条。易于移植,现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。模块化设计:RISC-V架构可以由不同模块组成不同功能,灵活利用模块的组合情况,可以定制属于自己需求的MCU。例如针对小面积低功耗的嵌入式场景,可以选择RV32IC组合的指令集,仅使用机器模式,就可以大大降低功耗和自身体积;而高性能的应用操作系统场景可以选择RV32IMFDC指令集,可以使用机器模式和用户模式,从而实现更高性能。完整的工具链:工具链对于CPU来说,就可以理解为螺丝刀对于螺丝,没有螺丝刀的作用,螺丝是根本无法固定住发挥自身的性能的。工具链是软件开发与CPU交互的窗口,如果没有工具链,软件开发者甚至无法让CPU工作起来。幸运的是,RISC-V由于贡献者多年的热心贡献,社区已经提供了完整的工具链,并且由RISC-V基金会维护该工具链。

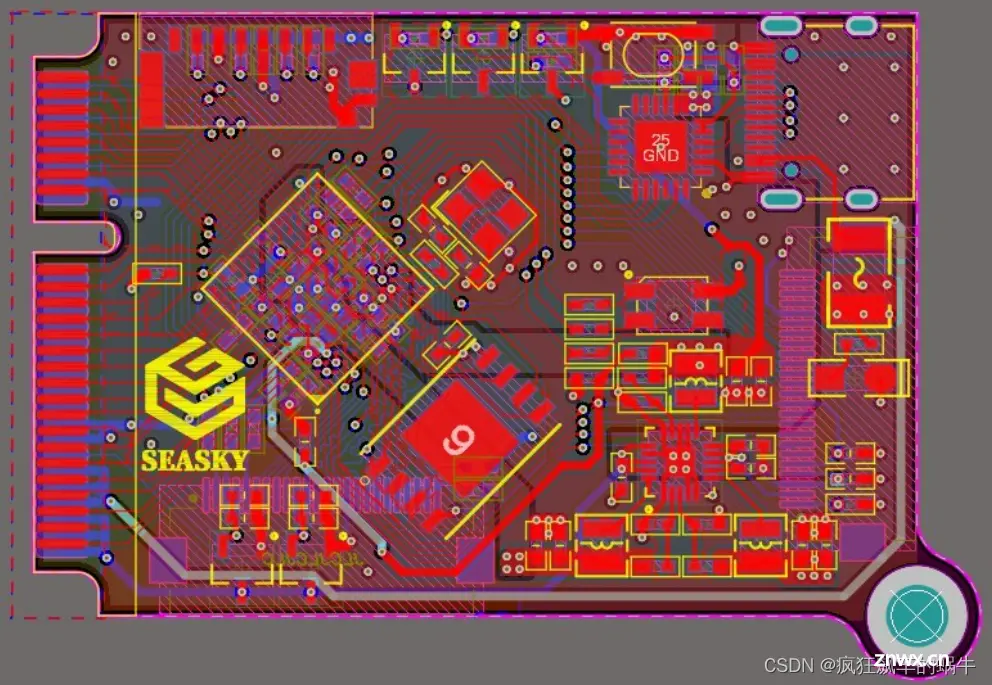

二、开发板介绍

嘉楠科技开发,设计,生产芯片,下游厂商将芯片做成开发板,通过硬件和解决方案进行销售;开发板有很多,可以从嘉楠科技购买评估板如:01Studio,缺点是比较贵;那就去看看其他下游厂商以此芯片做的开发板和解决方案吧,会便宜不少;

本开发版的软硬件全部开源,如有需要可以联系;先看下外观

总结

先大致介绍到这里吧,拿到开发板一起从零开始我们的AI嵌入式项目;

声明

本文内容仅代表作者观点,或转载于其他网站,本站不以此文作为商业用途

如有涉及侵权,请联系本站进行删除

转载本站原创文章,请注明来源及作者。