verilog vscode 与AI 插件

cnblogs 2024-09-12 08:13:00 阅读 77

Verilog 轻量化开发环境

背景

笔者常用的开发环境

- <li>VIAVDO, 体积巨大,自带编辑器除了linting 能用,编辑器几乎不能用,仿真界面很友好,但是速度比较慢。

- Sublime Text, 非常好用的编辑器,各种插件使用verilog 非常方便,可以自动补全、生成调用、linting等;

- VSCODE,Sublime Text 有的插件,VSCODE也都有,虽然不一定有sublime text好用,但是VSCODE有AI插件的加持,显得更有吸引力,更能提高工作效率。而且完全免费,VSCODE 注定一统江湖。

因此这里主要说明如何搭建VSCODE轻量化环境。

环境搭建

首先你得有VSCODE,安装包bing.com 搜索一下(不要问为什么不用百度) 自行安装即可。

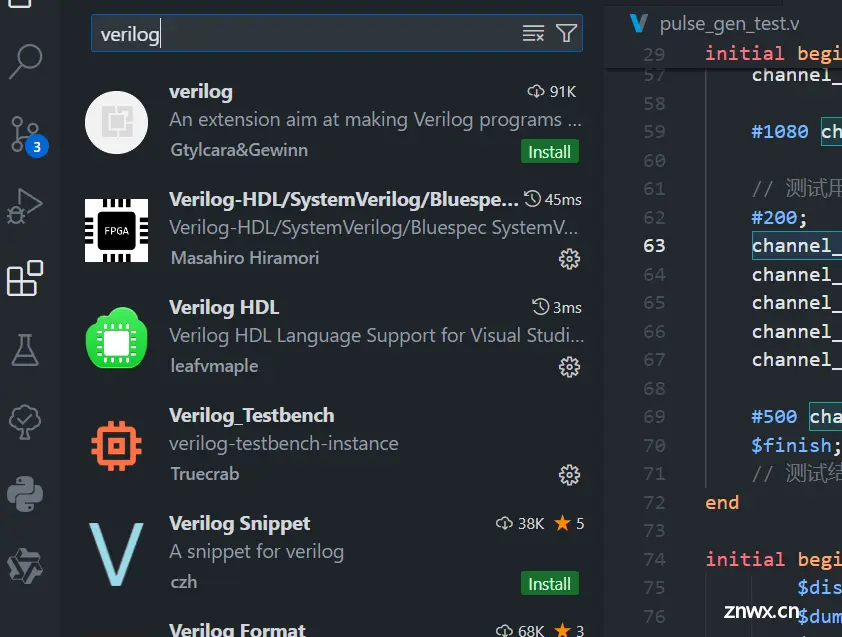

安装插件

图 2‑1 VSCODE Verilog 插件

安装Iverilog

Icarus Verilog for Windows (bleyer.org) 下载安装轻量级开发、编译工具Iverilog,这样就可以完全不用VIVADO就完成模块级的代码开发。

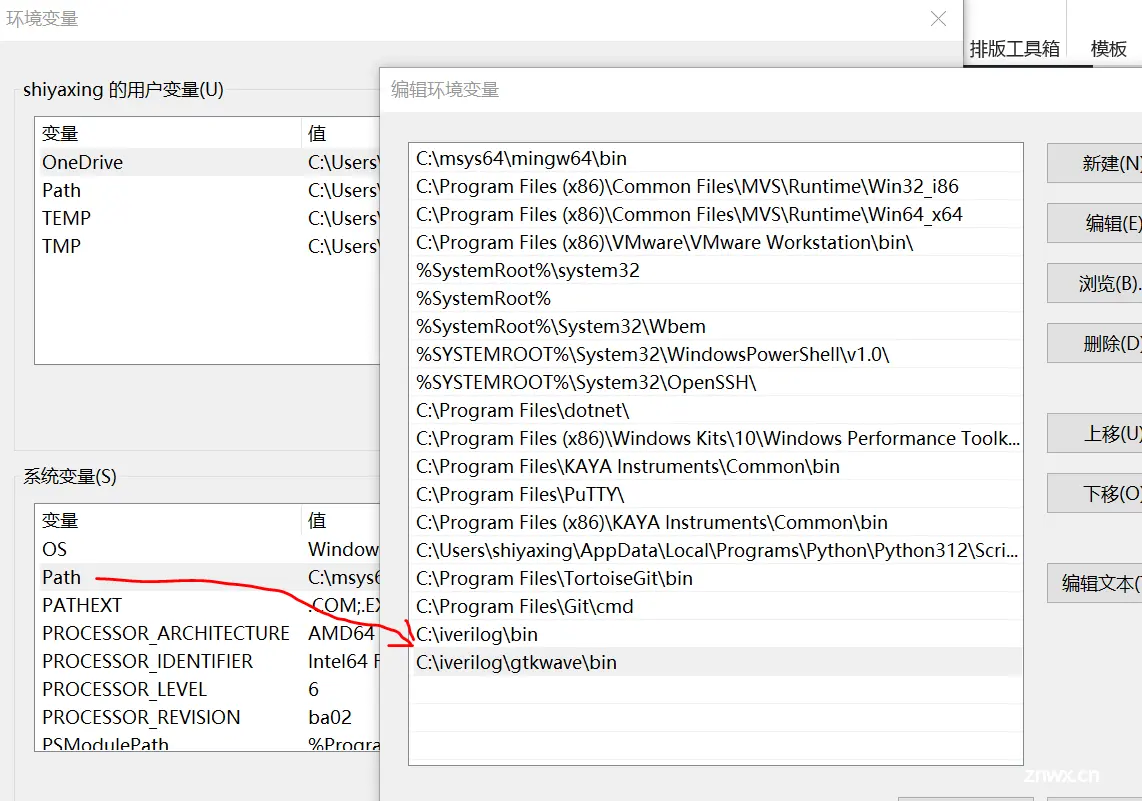

安装完成之后设置环境变量:

图 2‑2 设置iverilog 和 gtkwave 环境变量

设置完成重启 电脑, WIN11似乎不用重启 立即生效,只需要重启VSCODE

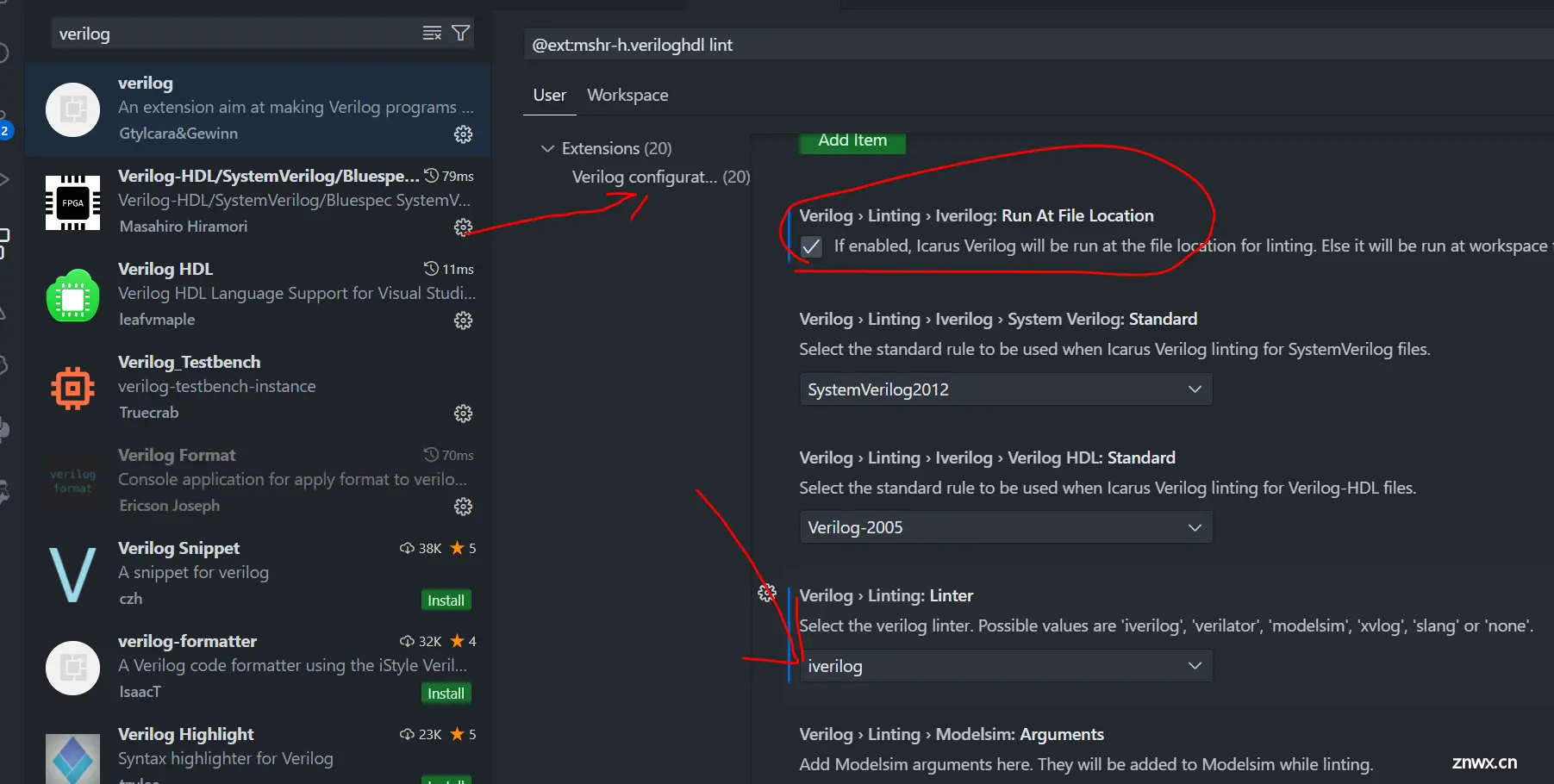

设置插件

图 2‑3 设置linter 为iverilog 运行在文件所在目录

编译 查看波形

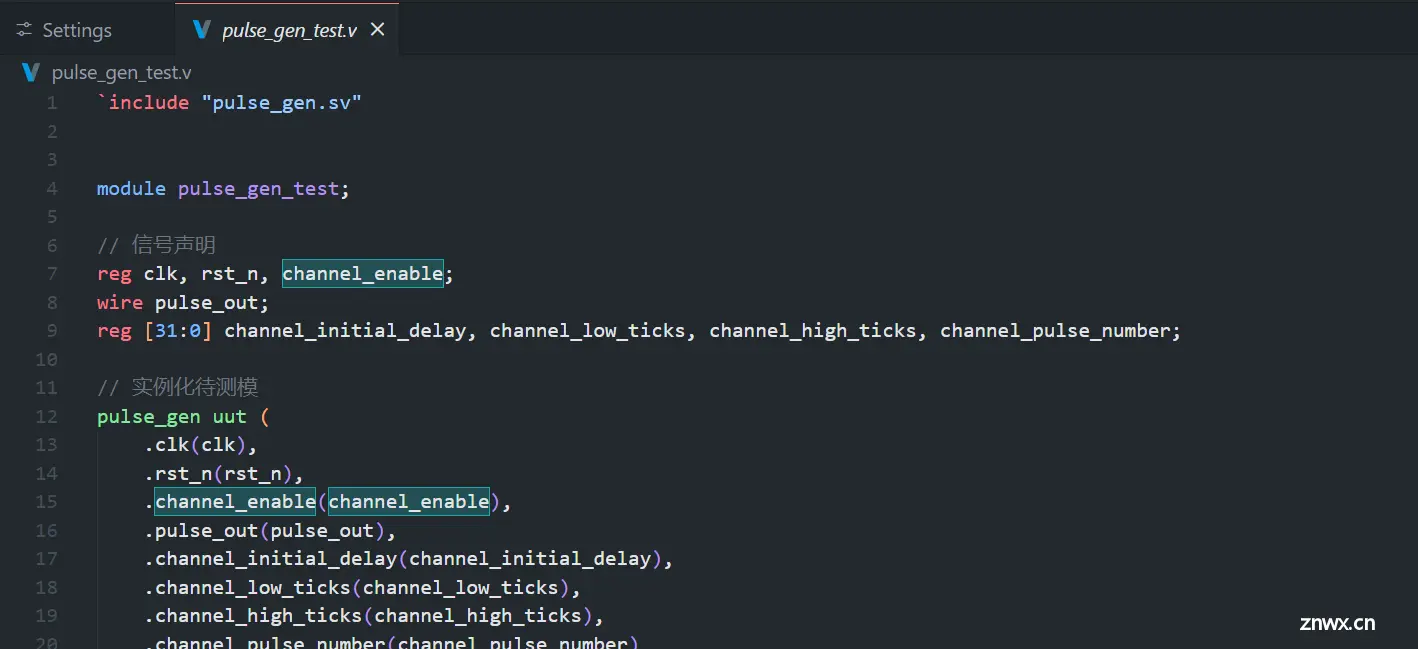

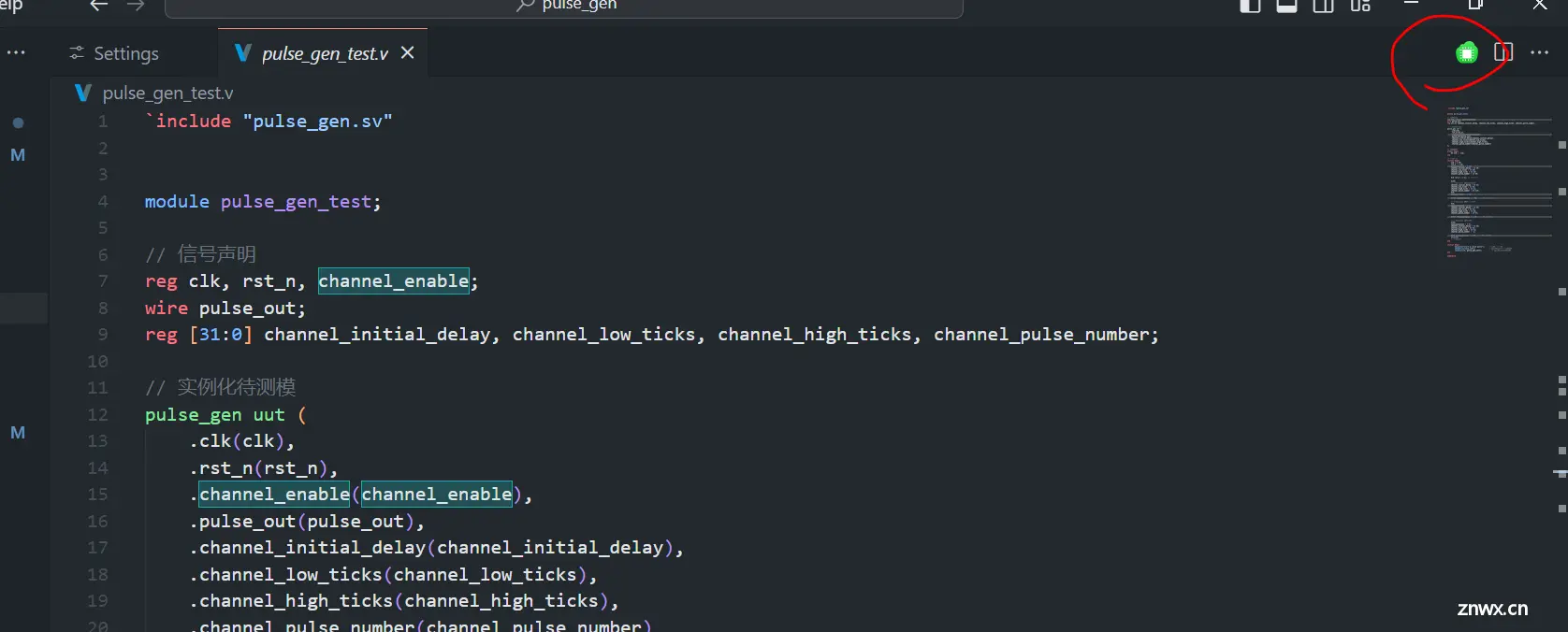

Iverilog 对.sv文件支持不好,需要编译的顶层文件最好是.v 后缀。涉及到模块调用,最好在代码中用`include 声明一下。

图 2‑4 仿真顶层

图 2‑5 运行编译 仿真

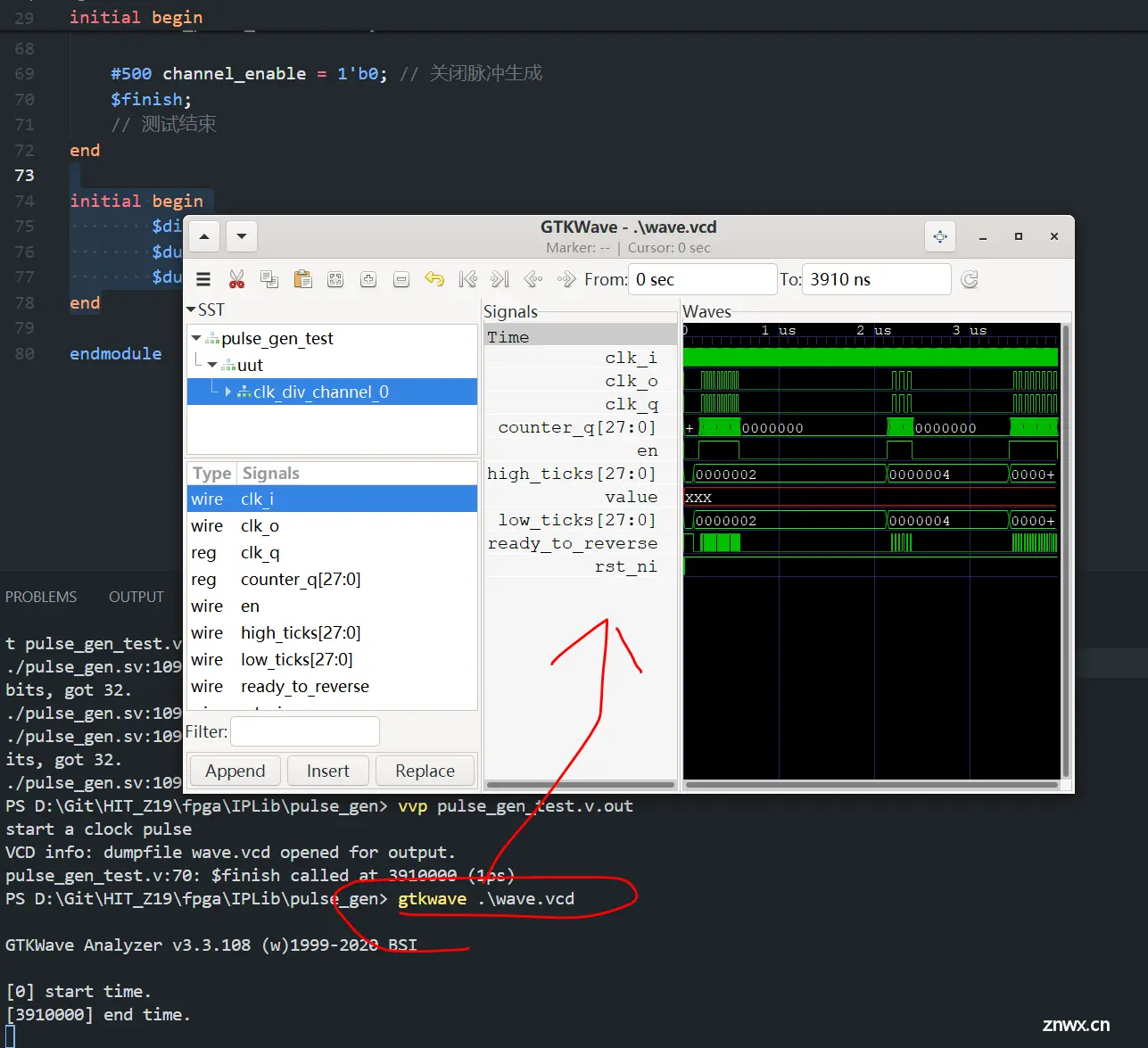

注意代码中必须包含自动$finish; 还要dump波形文件。

initial begin

$display("start a clock pulse"); // 打印开始标记

$dumpfile("wave.vcd"); // 指定记录模拟波形的文件

$dumpvars(0, pulse_gen_test); // 指定记录的模块层级

end

也可以用命令行运行编译和仿真,基本命令如下:

@echo off

iverilog.exe -o target.vvp pulse_gen_test.sv

vvp.exe target.vvp

其中-o是目标文件,pulse_gen_test.sv是待编译的仿真文件,vvp.exe执行对应的仿真。

然后生成目标wave.vcd文件,通过gtkwave 可以查看(在终端中执行gtkwave .\wave.vcd)。

图 2‑6 gtkwave 查看波形

需要说明,VSCODE中的自动实例化模块有点问题,希望后面插件可以解决。

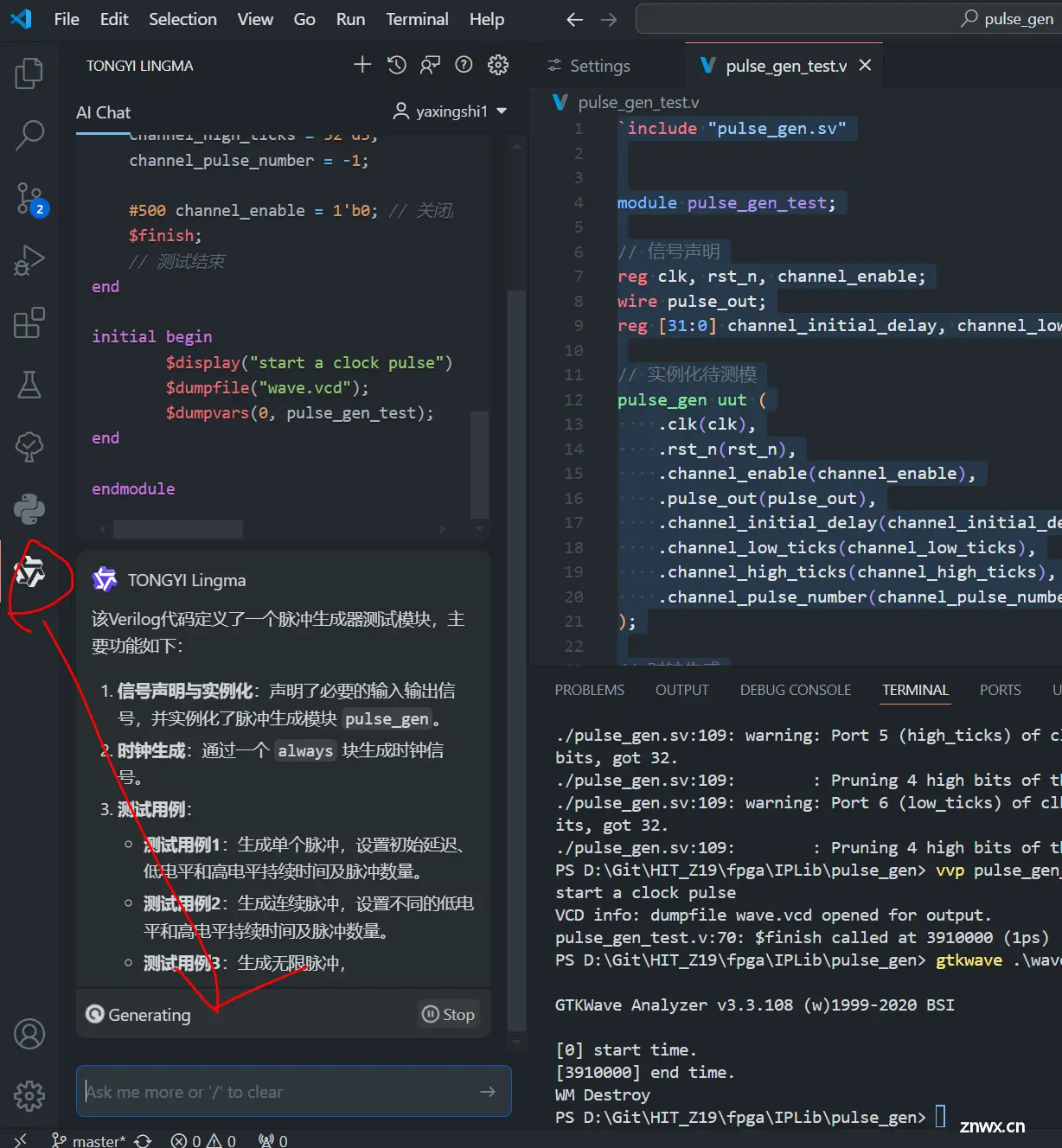

AI 插件

VSCODE最强的是他的AI插件,这个是sublime text 没有的。

图 3‑1 阿里TONGYI Lingma 插件

应用市场搜索安装即可,国内大模型和插件,阿里的最靠谱,实际使用体验不错,详细很快能够追上国外。

声明

本文内容仅代表作者观点,或转载于其他网站,本站不以此文作为商业用途

如有涉及侵权,请联系本站进行删除

转载本站原创文章,请注明来源及作者。